How to choose fpga programming language?

Introduction

FPGA (Field Programmable Gate Array) is a programmable logic device with flexibility and high performance. It can realize various digital circuits Q through programming, from simple logic gates to complex processors and even system-level designs. Understanding FPGA development languages is the key to learning FPGA programming. Engineers need to utilize a specific programming language to program an FPGA. While there are many programming languages for FPGAs, VHDL, Verilog, SystemVerilog, and C/C++ are the most often used ones.

This article will introduce the commonly used FPGA programming languages and their characteristics. For beginners, how to choose the appropriate FPGA programming language.

Table of Content

VHDL

VHDL is a high-level language used for circuit design. Mainly used in the field of digital circuits, in addition to statements containing a variety of hardware features, VHDL's hardware description language and its description style are similar to high-level computer languages. Its biggest features are powerful functions, strong design flexibility, multi-level design functions, wide support, and easy modification, and it is also easy to share and reuse. A good choice for beginners.

VHDL

Verilog

Verilog HDL is a hardware description language. It is mainly a language that describes the structure and behavior of digital system hardware in text. Through the use of Verilog HDL, it can express logic circuit diagrams, logical expressions, etc. It is also used in various digital systems from algorithm and gate levels to switch machines. Modeling.

The primary characteristic of Verilog HDL is its ease of learning and usage. You can pick up and master the C language quickly if you have programming experience with it. Therefore, Verilog HDL content can be arranged to be taught within courses related to ASIC design and so on. , Since the HDL language itself is specifically oriented to hardware and system design, this arrangement allows learners to gain experience in designing actual circuits at the same time. In comparison, VHDL is more difficult to learn. However, the freer syntax of Verilog HDL can also easily cause beginners to make some mistakes, so we should pay attention to this.

SystemVerilog

SystemVerilog is a fairly new language. Mainly based on the Verilog language, it combines the Hardware Description Language (HDL) with the modern High-Level Verification Language (HVL) and has recently become the language for next-generation hardware design and verification. In addition to being used as a high-level, abstract modeling language, SystemVerilog has another distinctive feature that can be combined with chip verification methodology, that is, it can be used as a language tool to implement the methodology. Using verification methodology can greatly enhance module reusability, improve chip development efficiency, and shorten the development cycle. The more famous chip verification methodologies include VMM, OVM, AVM UVM, etc.

C/C++

FPGAs are frequently programmed using the general-purpose programming language C/C++. Because C/C++ is a high-level language, it is simple to read and comprehend. Applications like computer vision and robotics, where performance is crucial, frequently use C/C++.

The versatility of C/C++ is one of its key benefits. It's ideal for more complex projects because it makes it simple for users to write and edit code. Moreover, C/C++ is highly portable due to its compatibility with other platforms. Because of this, it's excellent for developers who want to create apps for several platforms.

Verilog HDL VS VHDL: which one choose?

Verilog HDL and VHDL are languages for describing hardware circuit design. Their common features are: It can formally abstract the structure and behavior of circuits, support the description of levels and fields in logic design, and use the exquisite structure of high-level languages to simplify the description of circuits. It has circuit simulation and verification mechanisms to ensure the correctness of the design and support circuits. The description is a comprehensive conversion from high-level to low-level. The hardware description has nothing to do with the implementation process (relevant process parameters can be included through attributes provided by the language), which facilitates document management, easy understanding, and design reuse. However, Verilog HDL and VHDL have different features. Since Verilog HDL was launched as early as 1983 and has been used for thirteen years, Verilog HDL has a wider design community and has far more mature resources than VHDL.

The primary benefit of Verilog HDL over VHDL is its ease of learning as a hardware description language. As long as you have a programming foundation in C language, after twenty hours of study, plus a period of practical operation, you can generally master it in two to three years. Master this design technique within months. It is more difficult to master VHDL design technology. This is because Ada programming is a prerequisite for using VHDL, which is not very obvious. It is generally believed that it takes at least half a year of professional training and learning to master the basic design technology of VHDL.

The coverage of behavioral-level abstract modeling in the most recent iterations of Verilog HDL and VHDL varies as well. It is generally believed that Verilog HDL is slightly worse than VHDL in system-level abstraction, but much better than VHDL in gate-level switch circuit description.

Relatively speaking, VHDL is used more in Europe and is characterized by strict logic and caution. Verilog is commonly used in the United States and is characterized by its flexible syntax. There is not much difference in grammatical structure between the two, and they are generally the same. VHDL programs may appear bloated at first, but they will be easier to debug and modify later on. The FPGA programming language you select will depend on your specific circumstances.

Verilog vs. C/C++: which is better?

VERILOG is relatively close to the C language. If you are familiar with C, you can choose to use the Verilog HDL language. The basic syntax is very similar to C and is also very flexible. The VHDL language is relatively rigorous. But C/C++ is a general-purpose programming language, and Verilog is a language for describing hardware. Verilog is better suited for designing FPGA circuits, while C/C++ is better suited for applications where performance is critical, such as computer vision and robotics.

From Bitfoic's insight, there are a variety of FPGA programming languages available for beginners. Popular options include Verilog and VHDL because of their abundance of materials and ease of learning. Another excellent choice for more intricate designs is SystemVerilog, which has sophisticated features including real-time simulation and dynamic memory allocation. Lastly, C/C++ is an excellent option for programmers who want to create apps for several platforms. Every language has advantages and disadvantages of its own, so it's critical to select the best one for the job.

Infineon's profit decreases, memory Q2 contract price increase revised upwards5/9/2024 6

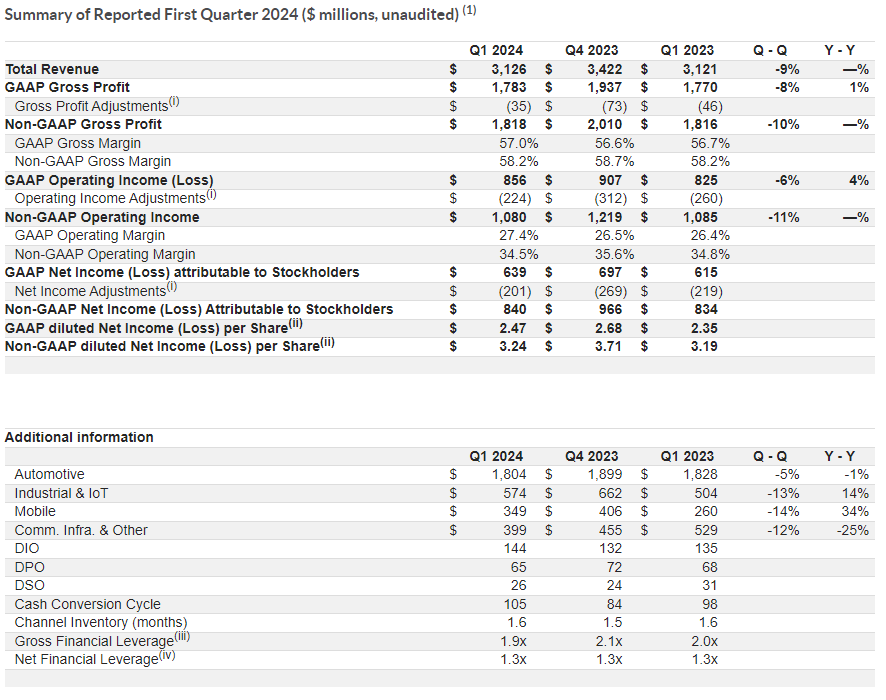

Infineon's profit decreases, memory Q2 contract price increase revised upwards5/9/2024 6Infineon recently announced its results for the second quarter of fiscal year 2024. Revenue was 3.632 billion euros, down 12% year-on-year and 2% month-on-month; profit was 707 million euros, down 40% year-on-year and 15% month-on-month; gross profit margin was 38.6%. , a year-on-year decrease of 8 percentage points and a month-on-month decrease of 4.6 percentage points.

Read More > NXP and ON Semiconductor released financial reports5/5/2024 25

NXP and ON Semiconductor released financial reports5/5/2024 25NXP and ON Semiconductor released financial reports, rising copper prices were transmitted to the IC industry

Read More > Tesla cuts 10% of global layoffs, Samsung increases NAND flash memory production this quarter4/17/2024 28

Tesla cuts 10% of global layoffs, Samsung increases NAND flash memory production this quarter4/17/2024 281.Tesla announced 10% of its global layoffs, with a higher domestic proportion

Read More > How much do you know about fpga design engineer?4/16/2024 54

How much do you know about fpga design engineer?4/16/2024 54Circuitry can be a complex field. The circuit must be completely redone because even the smallest error can drastically alter the project's outcome. One of the numerous individuals involved in circuit building is the FPGA design engineer.An electrical engineer with a focus on designing Field Programmable Gate Array integrated circuits is known as an FPGA engineer.After reading this site, you will be fully informed about fpga design engineers.

Read More > Renesas starts up old factory to increase power device production4/15/2024 32

Renesas starts up old factory to increase power device production4/15/2024 32Renesas Electronics announced in December that the Kofu factory that had previously ceased operations was reactivated. As a 300mm wafer fab, the plant will begin mass production of IGBTs and other products in 2025, doubling Renesas' current power semiconductor production capacity. Renesas held an opening ceremony on April 11, which was attended by local government officials and partner companies.

Read More >

Hot News

- Diode Overview: Application in Automotive Alternator Rectifiers

- Ultra-low power consumption of STM32U575/585 microcontrollers(MCU)

- The Best Guide to Transistor

- Basic Information about Temperature Sensor

- Voltage-Controlled Oscillator: Principle, Type Selection, and Application

- Electronic Component Symbols: Resistor, Capacitor, Transformers and Connectors